其中第一行为一个正整数 $n(n \le 5)$,表示元件的种类数,其后有连续的 $n$ 行,每行描述一种元件。对正整数 $1 \le k \le n$:

文件的第 $k+1$ 行有四个以空格隔开的整数,依次为:

$m_k$ $Y_{00}$ $Y_{01}$ $Y_{11}$

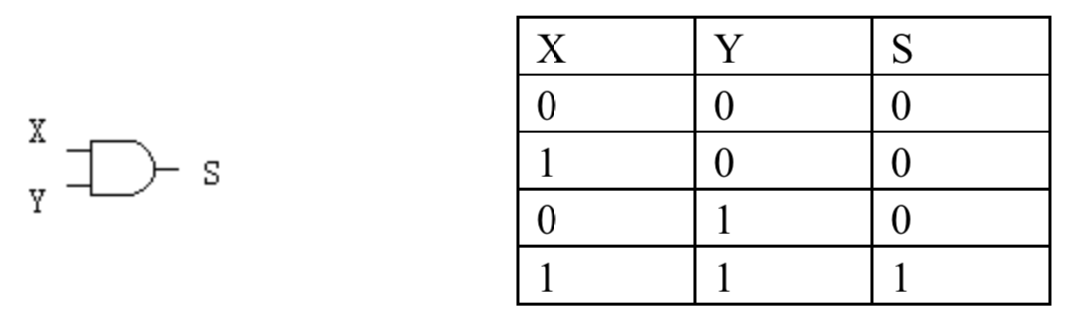

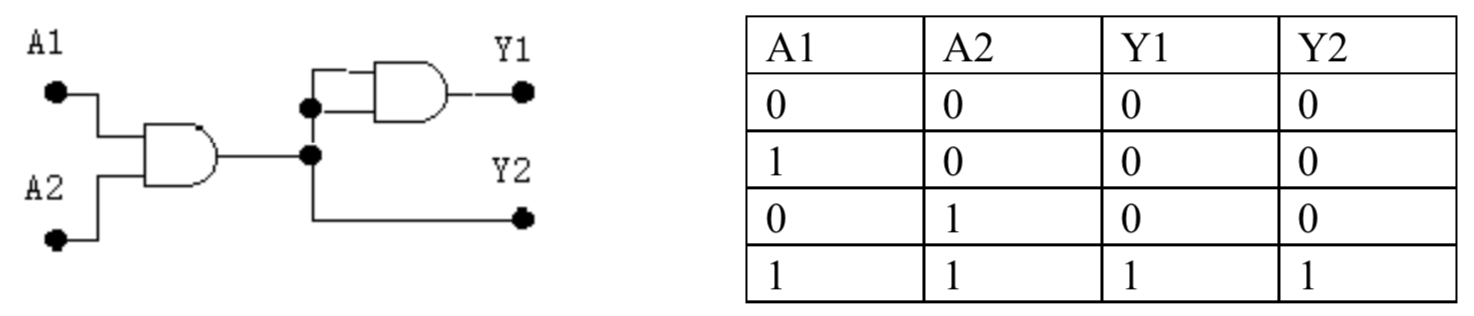

其中,正整数 $m_k$ 表示第 $k$ 种元件的数目($k$ 即这种元件的种类编号),所有元件的数目之和不会超过 $10$(用于实验的经费并不充足)。$Y_{ij}$ 表示两个输入端分别为 $i$ 和 $j$ 时的输出,即 $Y_{00}$ $Y_{01}$ $Y_{11}$ 是三个非 $0$ 即 $1$ 的数,分别表示在两个输入端均为 $0$;两个输入端一个为 $0$ 另一个为 $1$;以及两个输入端均为 $1$ 的时候,该元件的输出。

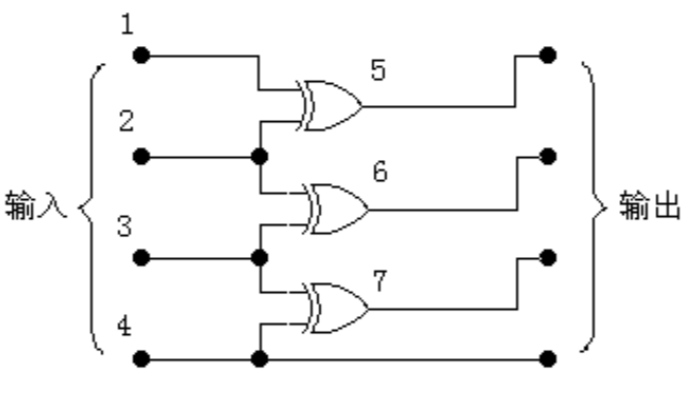

输入的第 $n+2$ 到第 $n+17$ 行,表示需组成的集成电路的功能表,每行有 $8$ 个数,分别为 $0$ 或 $1$。其中,前四个数依次对应四个输入端(编号为 $1$~$4$)的信号,不存在两行的前四个数完全相同;而后面四个数则对应在各输入端信号为前四个数时,四个输出端依次应输出的信号。